Memory Complier & Touchstone

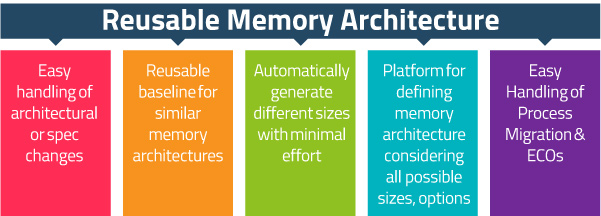

MC2, an automated and proven memory development system, targets embedded and discrete memories. MC2 automates the overall methodology for the design and distribution of memories, helping designers create solutions more rapidly. Empowering memory designers to design new memory instances, leverage existing designs, target new processes, create new memory architectures, MC2 increases productivity and promotes the reuse of design IPs. MC2 offers unique scalability for density as well as seamless migration to new sub-micron processes.

Customers using MC2 are expected to save over 40% of their development resources and time in the first project alone. Incremental savings can be expected over time. In addition, MC2 generates reusable memory architecture for secure distribution to ASIC & SoC designers.

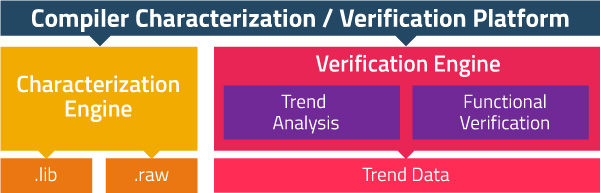

Touchstone is a characterization solution that provides timing and power parameters. The solution performs characterization at Instance (cell to lib) and compiler level and can be seamlessly integrated into any custom environment. The method of specification of characterization vectors is based on high level operations, e.g. read, write, etc. Tightly coupled with MC2, Touchstone provides options to present trends of calculated parameters.